editShanes post below has way more informative links

So a few of us decided to have a look inside the big green LED sign. We are curious about modernizing the hardware somewhat so you know, internet of things shenanigans can happen.

First step is figuring out how it works.

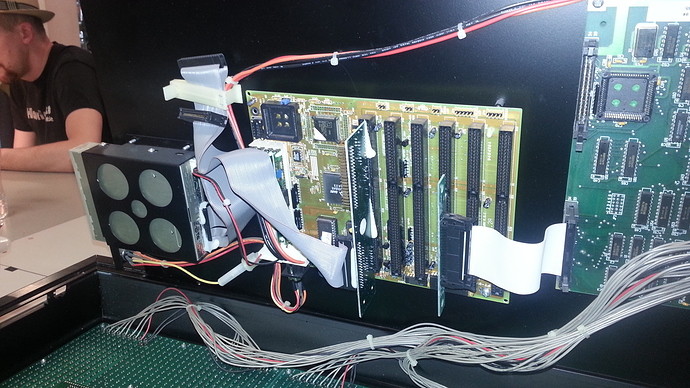

So here is the setup, a 386 pc with a leaky bios battery running custom firmware (which is rather limited in its options, thus reverse engineering the setup looks like a good idea), is connected via a passive ISA adapter card:

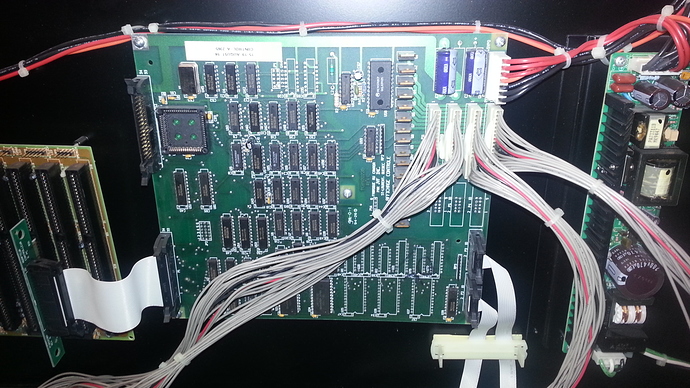

To a board containing a hodge podge of tri-state flip flops, line decoders, latches, and sram, I saw SN74HC574N, MC14514, LH5116-10 . There are also 16 IRFZ40 mosfets. This isn’t a complete list because this was more of a poke about and get a feel for it rather than a full reverse engineer fest.

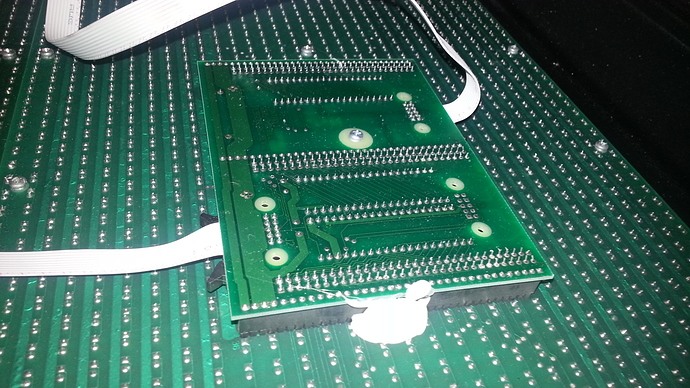

The heavy power cables next to the mosfets go to rails hooked up to the leds (forgot to note it if its common cathode or anode), and there are also 10 connector ribbon cables going to this board which is screwed and glued to the back of the led board:

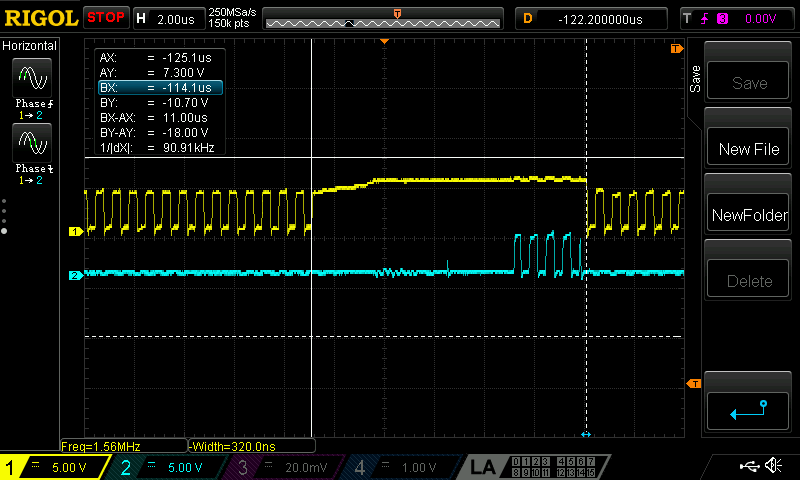

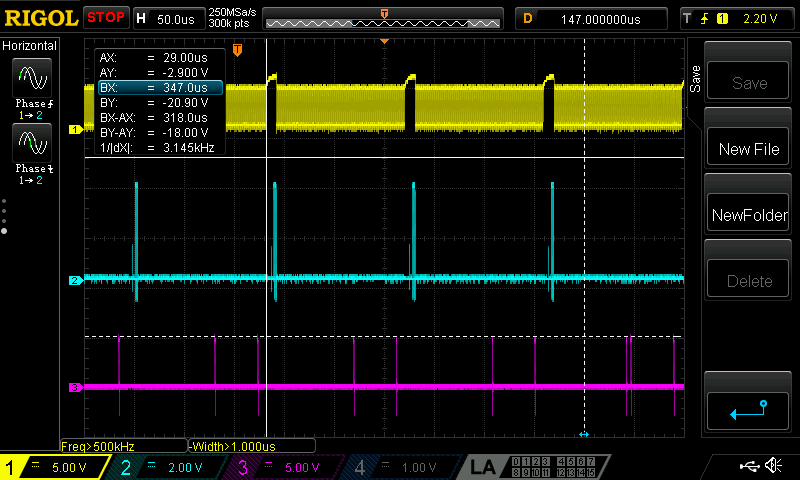

For entertainment, I scoped the first three lines off that 10 conductor ribbon cable (the other 7 appear to be ground, which seems odd, perhaps this is just in their latched state, should recheck this when its powered next time). Not the most useful result but hey this new scope is fun.

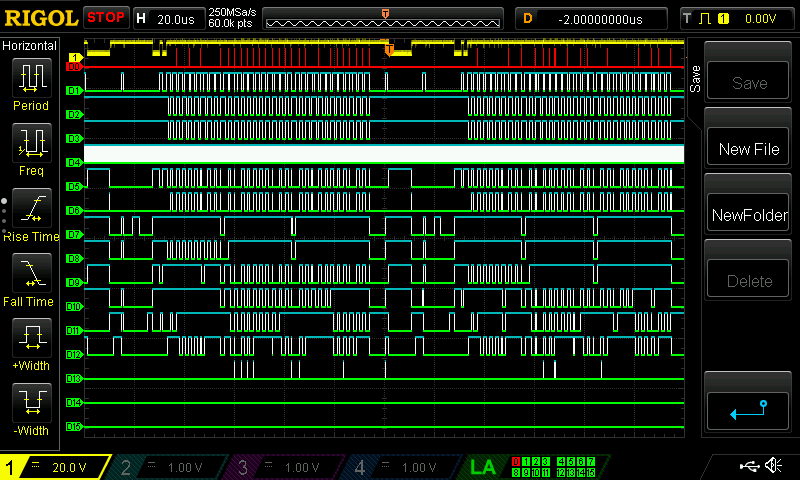

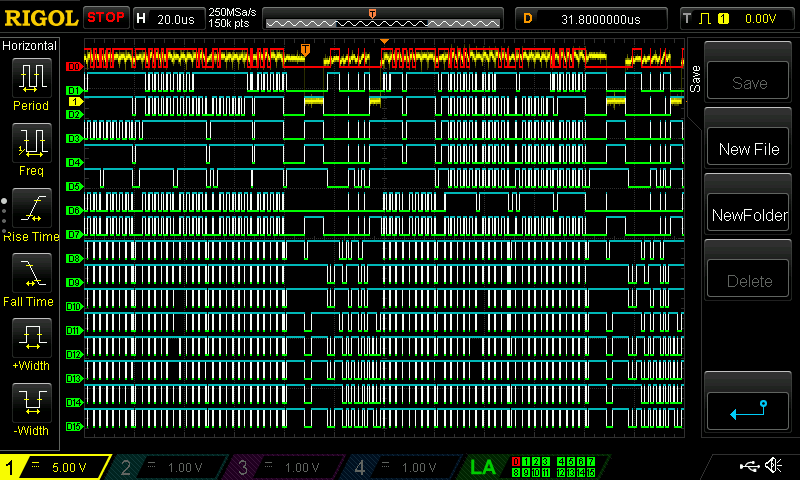

So yeah, I think my plan from here is to hook a logic analyzer up to that main ribbon cable coming off the ISA bus, and see what they protocol is. It might also be worthwhile to spend some time to figure out how they rigged their multiplexing and dimming scheme. It only has 16 mosfets and it seems to be able to individually dim each led (dim into 3 states, on, mid bright and off) so its using some sort of time domain switching.

If anyone has made it this far and has knowledge of how memory registers and flip flops and gates in this era were set up and what is likely to be the control scheme, feel free to chime in, because I have no idea what any of this does and am kinda winging it, or you know, learning.