Instructions to install Zedboard JTAG drivers in Linux:

http://svenand.blogdrive.com/archive/172.html

and don’t forget to do a reboot after

Z-Turn board:

The Z-Turn board IO Cape has a “camera” port labelled J2. It’s a CPI interface. The max resolution of CPI is 720p30

A possible camera is the BeagleBone Black HD Camera Cape

Thank you!

Next Week Saturday FPGA / RTOS lab work class will start at 15:00 and run until 19:00.

Thursday FPGA / RTOS Lecture class time will not change. It will start at 19:30 and run until 22:30

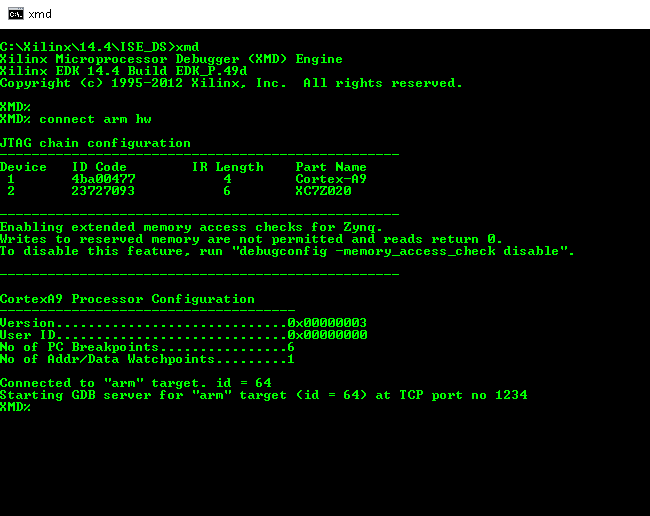

JTAG and Xilinx

Although openocd is able to flash the bitstream file to an FPGA (and consequently, you can use any JTAG device supported by openocd), openocd is not supported by the Xilinx development tools. This means openocd cannot be used with the debugging tools.

The bitstream file can also be loaded into the PL (programmable logic) in the Zynq devices by means of linux running on the arm cores, but debugging is not supported through this channel.

I have done a lot of research and have come to the conclusion that there are only two manufacturers of JTAG devices that are supported by the Xilinx toolchain: Xilinx and Digilent.

Therefore the available JTAG devices with debugging support are:

from Xilinx:

- I have left out all older devices that are not worth mentioning

- all Xilinx JTAG devices in this list support all Xilinx programmable logic ics, with the exception of top of the line high density, high speed devices (If you are programming those, why are you reading this? please come teach us!)

- features included: SPI support, IO voltages from 1.5 to 5V, 24Mhz max clock

- Xilinx is slowly removing support for the 24Mhz clock rate from the software tools as it is too sensitive to timing issues.

- XUP-USB JTAG: sold through Digilent with an academic discount $99, equivalent to the DLC9 series

- Platform Cable USB (DLC9): uses a CPLD X2C256, does not support HALT pin (used by Zynq series to debug the arm cores), clones can be bought on aliexpress for $25-$40

- Platform Cable USB (DLC9G): same as DLC9, but lead-free

- Platform Cable USB 2 (DLC10): Newest cable from Xilinx, supports the HALT pin required to debug arm cores in Zynq

From Digilent

- Support a variety of devices but designed primarily for use with Xilinx devices

- Max clock is 30Mhz ( see note about Xilinx discontinuing support for 24Mhz clocks due to timing requirements difficult to meet with JTAG devices )

- There are more digilent offerings but they either cost more or provide less features

- HS2:1.5-5V IO, Vivado 2012+, ISE 13.2+, 14-pin, 6-pin, 4-wire JTAG, 2-wire JTAG, SPI $60

- HS3:1.8-5V IO, Vivado 2012+, ISE 14.1+, 14-pin, no 6-pin, 4-wire JTAG, no 2-wire JTAG, SPI, supports HALT for Zynq arm core debugging (PS_RST) $60

- JTAG-SMT2: SMT module to add to your own design, supports all the features of HS2 and HS3 inclusive $55

Hacking

Xilinx:

Xilinx devices consist of an mcu and a programmable logic (PL) device. The code for the mcu resides in RAM and it is downloaded from the computer at runtime. The PL bitstream is stored in non-volatile storage in the device. However, Xilinx tools will query the device for the bitstream version, and if it’s old, it will update it. What this means is that cloning Xilinx programming devices is possible as Xilinx software can be fooled into delivering the software required to run on the cloned hardware. No need to extract firmware from read-locked devices.

Digilent:

Digilent licenses it’s JTAG core to OEMs for inclusion on dev boards. The zedboard, zybo, and pynq are no exceptions, they all have a built-in Digilent JTAG USB interface. Digilent also sells a module that will add JTAG USB functionality to your design ( the JTAG-SMT2 ).

Examining the schematics of the zedboard and pynq, I theorize that it should be possible to use the built-in JTAG sytem to program an external Xilinx device. To do this, the Zynq on the zedboard (or pynq) needs to be held in a reset state, then connect the appropriate JTAG pins on both the donor (zedboard) and recipient (third party board without JTAG functionality), then proceed to program. One caveat is to make sure the IO voltages of the recipient and the donor are matched. This may need disabling of the IO power supply on the donor and use the IO voltage from the recipient to power the JTAG IO.

Conclusion

If the hack above works, then the best option is to purchase a Pynq device for $65 ( Academic discount ) as that will not only get you a JTAG tool to use, but also another Zynq device to experiment with.

Otherwise, my vote is for the Digilent JTAG-SMT2, as it provides the most features for the lowest cost. One would need to provide the JTAG cable ( or wire pig-tail ), and connect them to the corresponding pins on the SMT module.

Thank you for your research.

My need for the JTAG is not as pressing, so the cheaper clones might work

even if they take a while to receive. As you know the HALT pin is not

accessible on the parallella.

However it would be very nice to get a one to share fairly quickly.

What is your thoughts on going shares you pay 1/2 $50, we pay 1/2 which is

$25 each on the JTAG from Digilent? And you keep it after we receive

cheaper programmers from aliexpress.

I am assuming that is also fine for Rahul.

The parallella uses the Adapteva to interface with the zynq, as result my

need is less pressing. This requires that I build the Adapteva gdb server.

Adapteva has very nice build tools on github, but absolutely no

documentation how to even start building them. I have been learning as I

go. If you have built lots of linux tools it all makes since, once you

happen to figure out where to start.

No idea if this is applicable or would even work but perhaps check out the Black Magic Probe.

It is getting close to being shipped from it’s Kickstarter

I just built one last night!! and have 10 spare pcbs for an SMD night but need to get permission from developer to use them. They do state that they support the cpu in the zynq. The firmware and schematic are open source, I know someone who built his own.

I’ve tackled a lot of this already. My parallella base board I designed has two jtag connectors on it, one takes the 20 pin 2.54mm ARM connector and works with a probe like the jlink. The other connector is the 14pin? 2mm connector used by xilinx on their jtag probes. I use a fake probe like the one below I bought direct from China. I could possibly lend it and the parallella base board for this workshop.

https://item.taobao.com/item.htm?spm=a230r.1.0.0.rjZGl7&id=20807028270&ns=1#detail

We are meeting this Thursday evening. I would be great to borrow your JTAG.

Thank you

Can someone pick it up from near the PNE?

I can make the trip out there tomorrow in the evening sometime after 18:00.

When is a good time?

@packetbob are you going to this event on Thursday, saw a comment about you going to vhs. Can I drop the cable at your place perhaps?

i’m not going to that event but i was planning to go on Thursday…

you can drop it off at my place and i’ll bring it to the FPGAers…

Thx Bob,

http://www.ebay.com/itm/292078053056?ul_noapp=true

Parallella on ebay for US$90, no details assume 7010.

Bob has the cable.

https://www.parallella.org/parallella-models/

Parallella-16 Micro ServerIt is not a preferred model,

If you find a

Parallella-16 Embedded Platfromwhich is the 7Z020 I would like to

purchase another.

Making excellent progress with the Altera DECA Max 10 board.

Please follow this hacks:fpga:altera_10 [Vancouver Hack Space]

This ABSOLUTELY requires the windows quartus. The linux version if quartus

is absolutely BROKEN!!

Basically instantaneous on my over powered laptop. Linux was taking hours.